Sự chỉ rõ

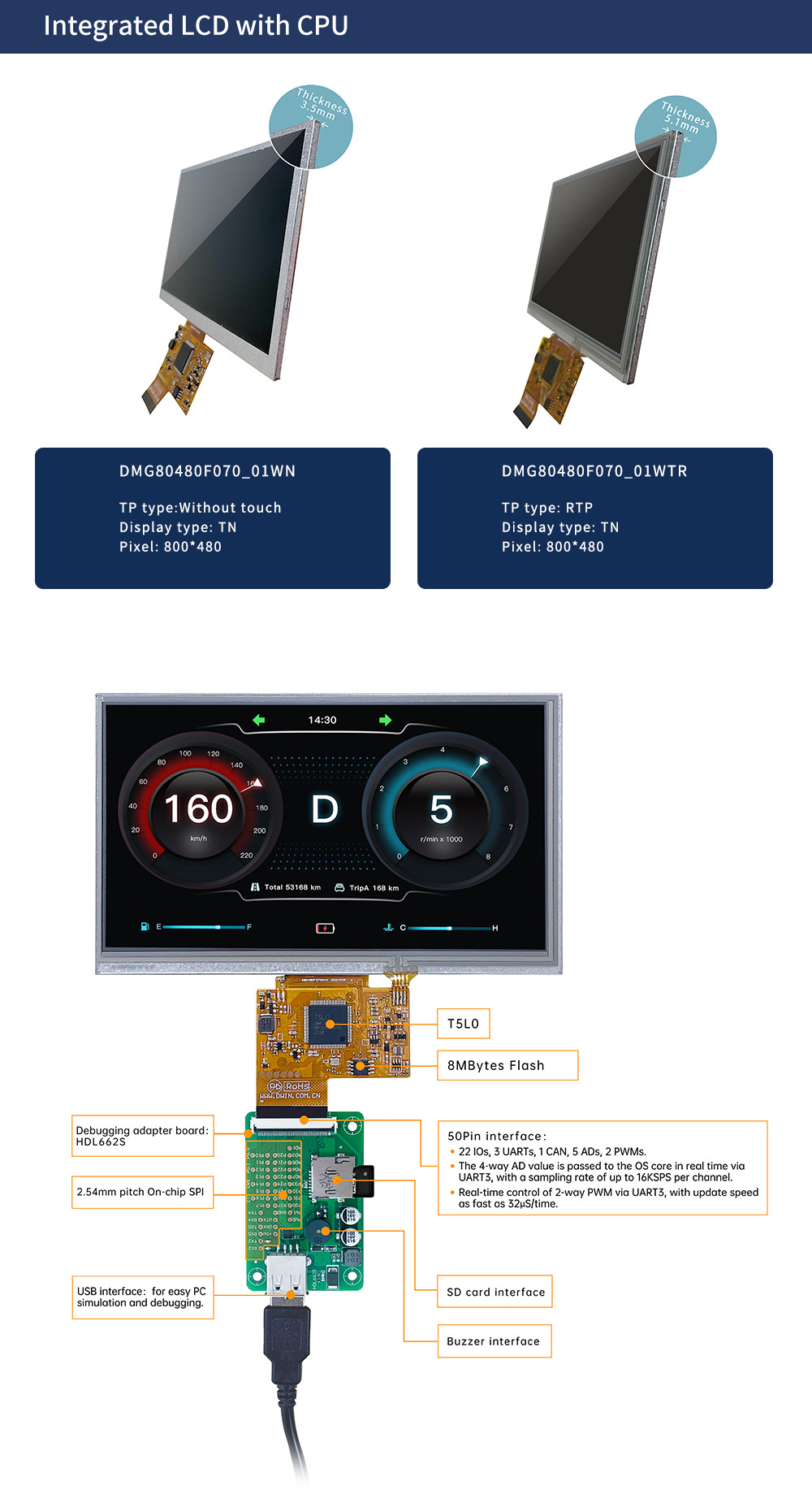

| ASIC T5L0 | Được phát triển bởi DWIN.Sản xuất hàng loạt vào năm 2020,1MBytes Nor Flash trên chip, không gian lưu trữ biến đổi 128Kbyte để trao đổi dữ liệu với Lõi CPU OS và bộ nhớ.Chu kỳ viết lại: hơn 100.000 lần | ||

| Màu sắc | 262K màu | ||

| Loại LCD | TN, TFT LCD | ||

| Góc nhìn | Góc nhìn bình thường, giá trị điển hình là 70°/70°/30°/40°(L/R/U/D) | ||

| Khu vực hiển thị(AA) | 154,08mm (Rộng)×85,92mm (C) | ||

| Nghị quyết | 800×480 | ||

| đèn nền | DẪN ĐẾN | ||

| độ sáng | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| Kiểu | RTP (Bảng cảm ứng điện trở) | ||

| Kết cấu | Phim ITO + kính ITO | ||

| Chế độ cảm ứng | Hỗ trợ chạm và kéo điểm | ||

| độ cứng bề mặt | 3H | ||

| truyền ánh sáng | Trên 80% | ||

| Mạng sống | Chấm > 1.000.000 lần;Đột quỵ > 100.000 lần;lực 150g, trở lại trở đi được tính là hai lần | ||

| điện áp | 3,6~5,5V | ||

| Hoạt động hiện tại | VCC = +5V, bật đèn nền, 410mA | ||

| VCC = +5V, Tắt đèn nền, 115mA | |||

| Nhiệt độ làm việc | -10℃~60℃ | ||

| Nhiệt độ bảo quản | -20℃~70℃ | ||

| Độ ẩm làm việc | 10%~90%RH, giá trị điển hình là 60%RH | ||

| Tốc độ truyền | 3150~3225600bps | ||

| Điện áp đầu ra | Đầu ra 1, Iout = 8mA;3.0~3.3V | ||

| Đầu ra 0, đầu ra = -8mA;0 ~ 0,3V | |||

| Điện áp đầu vào(XXD) | Đầu vào 1;3,3V | ||

| Đầu vào 0;0~0.5V | |||

| giao diện | UART2: TTL; | ||

| UART4: TTL;(Chỉ khả dụng sau khi cấu hình hệ điều hành) | |||

| UART5: TTL;(Chỉ khả dụng sau khi cấu hình hệ điều hành | |||

| Định dạng dữ liệu | UART2: N81; | ||

| UART4: N81/E81/O81/N82;4 chế độ (cấu hình hệ điều hành) | |||

| UART5: N81/E81/O81/N82;4 chế độ (cấu hình hệ điều hành) | |||

| Ổ cắm | FPC 50Pin_0,5mm | ||

| Tốc biến | 8 triệu byte | ||

| GHIM | Sự định nghĩa | vào/ra | mô tả chức năng |

| 1 | +5V | I | Nguồn điện, DC3.6-5.5V |

| 2 | +5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ADC đầu vào.Độ phân giải 12-bit trong trường hợp cấp nguồn 3,3V.Đầu vào 0-3,3V Vôn.Ngoại trừ AD6, dữ liệu còn lại được gửi đến lõi hệ điều hành thông qua UART3 trong thời gian thực với tốc độ lấy mẫu 16KHz.AD1 và AD5 có thể được sử dụng trong song song và AD3 và AD7 có thể được sử dụng song song, tương đương với hai AD lấy mẫu 32KHz.AD1, AD3, AD5, AD7 có thể được sử dụng song song, bằng với AD lấy mẫu 64KHz;dữ liệu được tổng hợp 1024 lần và sau đó chia cho 64 để thu được giá trị AD 16 bit 64Hz bằng cách lấy mẫu quá mức. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3.3 | O | Đầu ra 3.3V, tải tối đa 150mA. |

| 12 | SPK | O | MOSFET bên ngoài để điều khiển còi hoặc loa.Điện trở 10K bên ngoài nên được kéo xuống đất để đảm bảo bật nguồn ở mức thấp. |

| 13 | SD_CD | IO | Giao diện SD/SDHC, SD_CK kết nối tụ điện 22pF với GND gần giao diện thẻ SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O | 2 đầu ra PWM 16-bit.Điện trở 10K bên ngoài nên được kéo xuống nối đất để đảm bảo bật nguồn ở mức thấp.Lõi hệ điều hành có thể được điều khiển trong thời gian thực thông qua UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | IO | Nếu sử dụng RX8130 hoặc SD2058 I2C RTC để kết nối với cả hai IO, SCL phải được kết nối với P3.2 và SDA được kết nối song song với P3.3 với điện trở 10K kéo lên đến 3,3V. |

| 22 | P3.2 | IO | |

| 23 | P3.1/EX1 | IO | Nó có thể được sử dụng như một đầu vào 1 ngắt ngoài cùng một lúc và hỗ trợ cả chế độ ngắt mức điện áp thấp hoặc cạnh sau. |

| 24 | P3.0/EX0 | IO | Nó có thể được sử dụng như một đầu vào 0 ngắt bên ngoài cùng một lúc, và hỗ trợ cả chế độ ngắt mức điện áp thấp hoặc cạnh sau. |

| 25 | P2.7 | IO | giao diện IO |

| 26 | P2.6 | IO | giao diện IO |

| 27 | P2.5 | IO | giao diện IO |

| 28 | P2.4 | IO | giao diện IO |

| 29 | P2.3 | IO | giao diện IO |

| 30 | P2.2 | IO | giao diện IO |

| 31 | P2.1 | IO | giao diện IO |

| 32 | P2.0 | IO | giao diện IO |

| 33 | P1.7 | IO | giao diện IO |

| 34 | P1.6 | IO | giao diện IO |

| 35 | P1.5 | IO | giao diện IO |

| 36 | P1.4 | IO | giao diện IO |

| 37 | P1.3 | IO | giao diện IO |

| 38 | P1.2 | IO | giao diện IO |

| 39 | P1.1 | IO | giao diện IO |

| 40 | P1.0 | IO | giao diện IO |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | giao diện IO |

| 46 | P0.1 | IO | giao diện IO |

| 47 | CAN_TX | O | CÓ THỂ giao diện |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2(Cổng nối tiếp UART2 của nhân hệ điều hành) |

| 50 | UART2_RXD | I |